Add: 4th Floor Xiufeng Industrial Park, Buji Street, Longgang District, Shenzhen, China 518112 Tel: +86-755-28471034 Fax:+86-755-61824579 www.optinetec.com sales@optinetec.com

#### OP-X2-SFP+

### X2 to SFP+ converter Module

## **Features**

- ♦ Compatible with X2 MSA Rev.2.0b

- ♦ Case Temperature Range:

- ♦ Standard: 0°C ~70°C

- ◆ Duplex SC connector

- ♦ Hot pluggable 70 pin connector with XAUI electrical interface

- ♦ Management and control via MDIO 2 wire interface

- Complaint with the EU RoHS 6 Environmental Requirements

# Table 1-lists the SFP+ transceiver modules that can be plugged into the

## Converter Module.

| Product Name    | Product Description              |

|-----------------|----------------------------------|

| SR              | 850nm MM 10G SFP+                |

| LR              | 1310nm SM 10G SFP+ 10KM          |

| LRM             | 1310nm MM 10G SFP+ 2KM           |

| ER              | 1550nm SM 10G SFP+ 40KM          |

| ZR              | 1550nm SM 10G SFP+ 70KM          |

| CWDM            | CWDM SFP+ 10G                    |

| DWDM            | CWDM SFP+ 10G                    |

| BIDI            | SFP+ BIDI                        |

| All SFP+ Cables | SFP+ Cables, passive and active. |

# **Description**

The OP-X2-SFP+ a 10 Gigabit Ethernet X2 port into a 10 Gigabit Ethernet SFP+ port. With the converter module, customers have the flexibility to use the 10 Gigabit X2 interface port of a switch with X2 modules or SFP+ modules. This flexibility is critical when the specific type of interface is not available in one or the other form factor or when customers want to use the same form factor for interfaces across multiple platforms deployed in their network. It is a highly integrated, serial optical transponder module for high speed, 10Gbit/s data transmission applications. The module is fully compliant to IEEE 802.3ae standard for Ethernet, making it ideally suited for 10GbE datacom (rack to rack, client interconnection) applications. The transponder operates within a wide case temperature range of 0°C to +70°C and offers optimum heat dissipation and excellent electromagnetic shielding which enables high port densities for 10GbE systems. A 70 pin electrical connector and a duplex SC connector optical interface assure that connectivity is compliant to the X2 and XENPAK MSA.

Add: 4th Floor Xiufeng Industrial Park, Buji Street, Longgang District, Shenzhen, China 518112 Tel: +86-755-28471034 Fax:+86-755-61824579 www.optinetec.com sales@optinetec.com

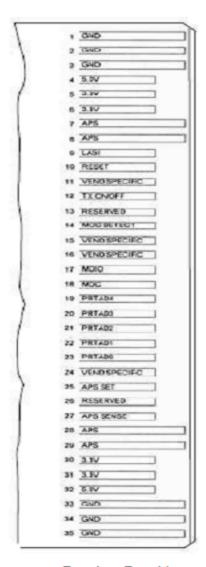

# **Card-Edge-Connector-Pinning and Layout**

Top view -Top side

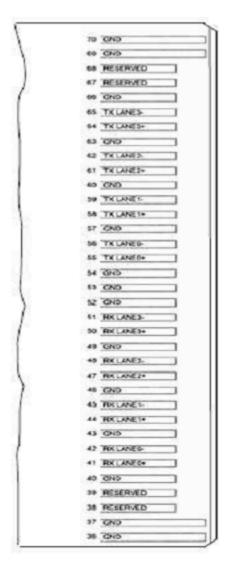

Top view-Bottom row

# **Table4-Electrical Pin Definition**

| Symbol    | Logic | PIN          | Name/Description                         | Note |

|-----------|-------|--------------|------------------------------------------|------|

| 3.3V      |       | 5, 6, 30, 31 | Power Supply of Optical Receiver and     | 2    |

|           |       |              | Transmitter and Control Circuits         |      |

| 5.0V      |       | 4, 32        | Power Supply of Optical Receiver         | 2    |

|           |       |              | Frontend                                 |      |

| APS       |       | 7, 8, 28, 29 | Adaptive Power Supply, Supply of PHY     | 2    |

|           |       |              | XS and PCS Layer Devices                 |      |

| APS SENSE |       | 27           | APS Sense Output for APS Control Circuit |      |

| APS SET   |       | 25           | Feedback Input for APS, Input of APS     |      |

|           |       | 25           | Setting Resistor                         |      |

| GND       |       | 1, 2, 3, 33, | Common Electrical Ground                 | 1    |

Optinet Technology Co., Ltd

Add: 4th Floor Xiufeng Industrial Park, Buji Street, Longgang District, Shenzhen, China 518112

Tel: +86-755-28471034 Fax:+86-755-61824579

www.optinetec.com sales@optinetec.com

|              |        |                 | etec.com sales@optinetec.com                         |   |

|--------------|--------|-----------------|------------------------------------------------------|---|

|              |        | 34, 35, 36,     |                                                      |   |

|              |        | 37, 40, 43,     |                                                      |   |

|              |        | 46, 49, 52,     |                                                      |   |

|              |        | 53, 54, 57,     |                                                      |   |

|              |        | 60, 63, 66,     |                                                      |   |

|              |        | 69, 70          |                                                      |   |

| LASI         | 1.2V   | 9               | Link Alarm Status Interrupt, low active,             |   |

|              | CMOS   | · ·             | Open Drain Output Supposed to operate                |   |

|              | Open   |                 | with 10KL 22KL pull upon host. Logic                 |   |

|              | •      |                 |                                                      |   |

|              | Drain  |                 | High: Normal Operation                               |   |

|              | Output |                 | Logic Low: Link Alarm is indicated                   | _ |

| MDC          |        | 18              | Management Clock Input                               | 3 |

| MDIO         |        | 17              | Management Data                                      | 3 |

| MOD DETECT   |        | 14              | 1kL to Ground for APS Circuit                        |   |

| WOD DETECT   |        | 1-7             | Environment                                          |   |

|              | 1.2V   |                 | Dout Address Dit 0 (Low = 0) internally              |   |

| PRTADO       | CMOS   | 23              | Port Address Bit 0 (Low = 0), internally             |   |

|              | Input  |                 | pulled up by 18kL                                    |   |

|              | 1.2V   |                 |                                                      |   |

| PRTAD1       | CMOS   | 22              | Port Address Bit 1 (Low = 0), internally             |   |

|              | Input  |                 | pulled up by 18kL                                    |   |

|              | 1.2V   |                 |                                                      |   |

| DDTAD2       |        | 21              | Port Address Bit 2 (Low = 0), internally             |   |

| PRTAD2       | CMOS   | 21              | pulled up by 18kL                                    |   |

|              | Input  |                 |                                                      |   |

|              | 1.2V   |                 | Port Address Bit 3 (Low = 0), internally             |   |

| PRTAD3       | CMOS   | 20              | pulled up by 18kL                                    |   |

|              | Input  |                 | L                                                    |   |

|              | 1.2V   |                 | Port Address Bit 4 (Low = 0), internally             |   |

| PRTAD4       | CMOS   | 19              | pulled up by 18kL                                    |   |

|              | Input  |                 | pulled up by Toke                                    |   |

| DEOED\/ED    |        | 13, 38, 39, 67, | Reserved by MSA, internally not                      |   |

| RESERVED     |        | 68              | connected                                            |   |

|              |        |                 | Reserved for Avalanche Photodiode use,               | _ |

| RESERVED     |        | 26              | internally not connected                             | 5 |

|              |        |                 | Low active Reset Input                               |   |

|              | 1.2V   |                 | 10KL pull up on Transceiver                          |   |

| RESET        | CMOS   | 10              | Logic high = Normal Operation                        |   |

|              | Input  |                 | Logic Low = Reset asserted                           |   |

|              |        |                 | -                                                    |   |

|              | 4.0\/  |                 | High active Transmitter Enable Input                 |   |

| TV 01/055    | 1.2V   | 40              | 10KL pull up on Transceiver                          |   |

| TX ON/OFF    | CMOS   | 12              | Logic high = Transmitter active (normal              |   |

|              | Input  |                 | Operation) And Register Bit 1.9.0 set to low as well |   |

|              |        |                 | Logic Low = shut down of Transmitter                 |   |

| VENDSPECIFIC |        | 11, 15, 16, 24  | Vendor Specific Pin,. for proper operation           | 5 |

Add: 4th Floor Xiufeng Industrial Park, Buji Street, Longgang District, Shenzhen, China 518112 Tel: +86-755-28471034 Fax:+86-755-61824579

www.optinetec.com sales@optinetec.com

|           |    | leave unconnected          |   |

|-----------|----|----------------------------|---|

| RX LANE0+ | 41 | Module XAUI Output Lane 0+ | 4 |

| RX LANE0  | 42 | Module XAUI Output Lane 0  | 4 |

| RX LANE1+ | 44 | Module XAUI Output Lane 1+ | 4 |

| RX LANE1- | 45 | Module XAUI Output Lane 1- | 4 |

| RX LANE2+ | 47 | Module XAUI Output Lane 2+ | 4 |

| RX LANE2- | 48 | Module XAUI Output Lane 2  | 4 |

| RX LANE3+ | 50 | Module XAUI Output Lane 3+ | 4 |

| RX LANE3- | 51 | Module XAUI Output Lane 3  | 4 |

| TX LANE0+ | 55 | Module XAUI Input Lane 0+  | 4 |

| TX LANE0- | 56 | Module XAUI Input Lane 0   | 4 |

| TX LANE1+ | 58 | Module XAUI Input Lane 1+  | 4 |

| TX LANE1- | 59 | Module XAUI Input Lane 1   | 4 |

| TX LANE2+ | 61 | Module XAUI Input Lane 2+  | 4 |

| TX LANE2- | 62 | Module XAUI Input Lane 2   | 4 |

| TX LANE3+ | 64 | Module XAUI Input Lane 3+  | 4 |

| TX LANE3- | 65 | Module XAUI Input Lane 3   | 4 |

<sup>1)</sup> Ground connections are common for TX and RX.

- 2) Each connector contact is rated at 0.5A.

- 3) MDIO and MDC timing must comply with IEEE 802.3ae clause 45.3.

- 4) XAUI output characteristics comply with IEEE 802.3ae clause 47.

- 5) Transceivers will be MSA compliant when no signals are present on the vendor specific pins.

## **Thermal Management**

The transponder is designed for an operation within a case temperature range between 0 to +70°C at an altitude of < 3km. The built in heatsink provides an optimized thermal performance. The user needs to guarantee per system design not to exceed this temperature range. It has to be considered that in case of usage of multiple modules on a single hostboard that there is a temperature rise among the modules hosted side by side. Airflow direction and air speed needs to be choosen accordingly. For further information it is referred to the MSA document.

## **Ordering information**

| Part Number | Product Description             |

|-------------|---------------------------------|

| OP-X2-SFP+  | 10G X2 to SFP+ Converter Module |